DesignWare ARC nSIM 17/09/2013 14:55

For the ARC EM family, the JIT compilation engine can be combined with an efficient micro-architectural performance model of the ARC processor pipeline. This enables near cycle-accurate simulation with a cycle accuracy of 95% (compared to RTL) at simulation speeds of over 25 MIPS, making it the ideal solution for high-speed architectural exploration and system profiling. In case a full 100% cycle accuracy is needed for the final performance tweaking, it is easy to switch over to the DesignWare ARC xCAM models that are derived from the processor's Verilog to achieve 100% cycle accuracy.

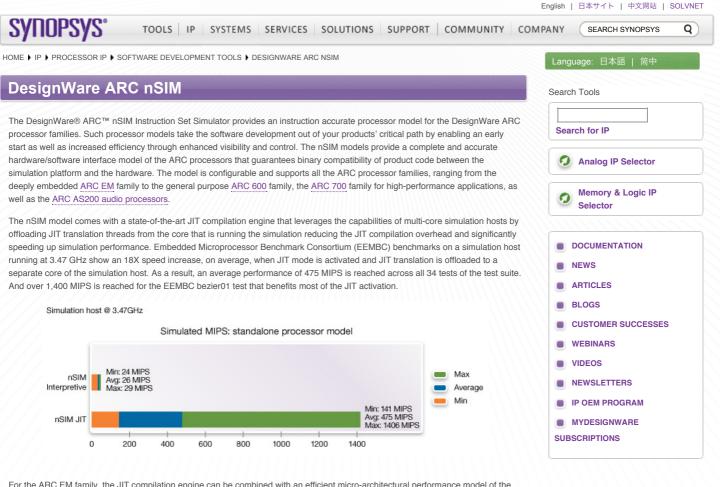

|                                                                                         | Interpretive                                                              | JIT                         |                                                                                                                                     |

|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Instruction\ Register\ Programmers View Accurate (Instruction Set Architecture model)   | Base mode<br>Avg. 20 MIPS                                                 | Turbo mode<br>Avg. 475 MIPS | SW development and<br>debugging<br>Function and<br>instruction accurate<br>profiling and optimization                               |

| Near Cycle-Accurate<br>(micro-architectural<br>processor pipeline<br>performance model) | NCAM turbo mode <sup>1</sup><br>Avg. 25 MIPS,<br>up to 95% Cycle Accuracy |                             | Cycle Approximate<br>profiling and optimization<br>High-speed Architectural<br>exploration and system<br>profiling and optimization |

While it is possible to run the NCAM Turbo model in Interpretive mode, doing so does not add value as it will only reduce simulation performance without adding accuracy.

Table 1: DesignWare ARC nSIM offers three modes of operation that you can switch between to balance performance and accuracy depending on the specific demands of your application. Listed performance numbers are average across 34 EEMBC tests, in standalone processor mode operation.

The nSIM processor model is delivered as a single DLL that integrates seamlessly with the <a href="MetaWare">MetaWare</a> and <a href="MetaWare">GNU</a> debuggers. Switching between the different operating modes like JIT or NCAM is as easy as invoking the model with the appropriate command-line parameter. The nSIM models come with an industry-standard OSCI TLM-2.0 SystemC interface to support their integration with OSCI standard peripheral models. In addition, the nSIM models implement the required interfaces for deployment in the <a href="Synopsys\_Synthmatrix">Synopsys\_Synthmatrix</a> Virtualizer platform, a tool for the creation, assembly and execution of SystemC-based virtual prototypes for pre-silicon software development and software-driven verification.

DesignWare ARC nSIM 17/09/2013 14:55

Order the DesignWare ARC nSIM Turbo or nSIM NCAM Turbo

▶ DesignWare ARC nSIM Instruction Set Simulator Datasheet

Highlights

End User Agreement

Products

Downloads and Documentation

- Single model supporting the ARC EM, ARC 600, ARC 700 and ARC AS200 families

- Available in standalone mode for processor centric algorithm development and performance tuning at highest simulation speed

- OSCI TLM-2.0 SystemC standard interface for integration with OSCI standard peripheral models

- Virtualizer integration layer provide access to advanced debugging and profiling capabilities offered by Virtualizer

- Very high speed JIT mode benefits from multi-core simulation hosts: 475 MIPS simulated performance for the EEMBC test suite on the ARC nSIM model for the ARC EM family

- High-speed near cycle-accuracy for system profiling and architectural exploration: up to 95% accuracy compared to RTL at over 25 MIPS (ARC EM family only)

- Seamless switching between different simulation modes by simple debugger command-line invocation

- Available for 32/64 bit Windows and Linux simulation hosts

- Models for EIA processor extensions and custom instructions can be added as an extension DLL or as a separate SystemC component

© 2013 Synopsys, Inc. All Rights Reserved.

Contact us | Locations | Privacy | Legal